## Информационные системы. Информатика. Проблемы информационной безопасности Information systems. Computer sciences. Issues of information security

УДК 681.3 https://doi.org/10.32362/2500-316X-2025-13-1-49-58 EDN JQICRJ

НАУЧНАЯ СТАТЬЯ

## Технико-экономический анализ серверов как вычислительных модулей вычислительных систем класса WSC

### Г.В. Петушков <sup>®</sup>, А.С. Сигов

МИРЭА – Российский технологический университет, Москва, 119454 Россия <sup>®</sup> Автор для переписки, e-mail: petushkov@mirea.ru

#### Резюме

**Цели.** Целью работы является технико-экономический анализ серверов как вычислительных модулей вычислительных систем (BC) класса WSC (warehouse scale computer).

**Методы.** Основные результаты работы получены с использованием методов математического анализа и моделирования.

Результаты. Проведен технико-экономический анализ вычислительных модулей или серверов на базе микропроцессоров класса Xeon (Intel, CШA) и им подобных. Приведен обзор подклассов микропроцессоров с указанием основных областей их использования, а также вариантов организации серверов и их основных составляющих. Надежность – комплексное свойство, которое, в зависимости от назначения объекта и условий его применения, может включать безотказность, долговечность, ремонтопригодность и сохраняемость или определенные сочетания этих свойств. Для обеспечения максимальной надежности сервера используют как резервирующие элементы – массивы дисков и блоков питания, так и резервные серверы, и специальные решения: использование горячей замены и подключения, методы повышения надежности оперативной памяти Error Checking and Correction для коррекции ошибок модулей оперативной памяти, контроль температурных режимов отсеков сервера.

**Выводы.** Проведенный обзор вариантов организации серверов и их основных составляющих позволяет сделать вывод о достаточно высокой надежности их функционирования. От серверов, объединенных в ВС класса WSC, как от системы, требуется непрерывность функционирования в режиме 24/7 в течение длительного времени. Это требует разработки методик оценки надежности таких высоконадежных систем, включающих резервные элементы, по отношению к отказам аппаратуры и программного обеспечения, а также методик прогнозирования отказов и мер борьбы с их последствиями.

**Ключевые слова:** надежность, резервирующие элементы, подклассы микропроцессоров, error checking and correction, коррекция ошибок, массив дисков, класс WSC

• Поступила: 18.10.2024 • Доработана: 22.11.2024 • Принята к опубликованию: 09.12.2024

**Для цитирования:** Петушков Г.В., Сигов А.С. Технико-экономический анализ серверов как вычислительных модулей вычислительных систем класса WSC. *Russian Technological Journal*. 2025;13(1):49–58. https://doi.org/10.32362/2500-316X-2025-13-1-49-58, https://www.elibrary.ru/JQICRJ

**Прозрачность финансовой деятельности:** Авторы не имеют финансовой заинтересованности в представленных материалах или методах.

Авторы заявляют об отсутствии конфликта интересов.

#### RESEARCH ARTICLE

# Technical and economic analysis of servers as computing system modules of the warehouse scale computer class

### Grigory V. Petushkov <sup>®</sup>, Alexander S. Sigov

MIREA – Russian Technological University, Moscow, 119454 Russia <sup>®</sup> Corresponding author, e-mail: petushkov@mirea.ru

#### **Abstract**

**Objectives.** The work set out to technically and economically analyze servers as computing modules of computing systems of the warehouse scale computer (WSC) class.

Methods. The research was carried out using the methods of mathematical analysis and modeling.

**Results.** The article provides a technical and economic analysis of computing modules or servers. Servers are created on the basis of Xeon (Intel) class microprocessors and the like. An overview of the microprocessor subclasses is given along with an indication of server organization options, as well as their main components and primary areas of use. Server reliability is a complex property that may include durability, maintainability and persistence, or certain combinations of these properties depending on the purpose of the object and the conditions of its use. To ensure maximum reliability, backup elements, including arrays of disks and power supplies, as well as backup servers, are used alongside special solutions, including the use of hot swapping and connection, checking and correction of random access memory errors, and temperature control of server compartments.

**Conclusions.** The review of options for organizing servers and their main components allows permits the conclusion that their operation is sufficiently reliable. However, servers integrated into the WSC class have special requirements, namely, continuity of operation in 24/7 mode for long periods of time. This requires the development of methods for assessing the reliability of such highly reliable systems, including backup elements, in relation to hardware and software failures, as well as methods for predicting failures and measures to combat their consequences.

**Keywords:** reliability, backup elements, MP subclasses, error checking and correction, error correction, disk array, WSC class

#### • Submitted: 18.10.2024 • Revised: 22.11.2024 • Accepted: 09.12.2024

**For citation:** Petushkov G.V., Sigov A.S. Technical and economic analysis of servers as computing system modules of the warehouse scale computer class. *Russian Technological Journal*. 2025;13(1):49–58. https://doi.org/10.32362/2500-316X-2025-13-1-49-58, https://www.elibrary.ru/JQICRJ

Financial disclosure: The authors have no financial or proprietary interest in any material or method mentioned.

The authors declare no conflicts of interest.

#### **ВВЕДЕНИЕ**

Сервер обладает множеством характеристик, таких как надежность, производительность, формфактор, энергопотребление и др. Эти характеристики часто складываются из набора свойств отдельных узлов, из которых состоит сервер [1].

Производительность, наряду с надежностью, является одной из ключевых характеристик сервера. Она определяется, в основном, объемом и скоростью вычислений и зависит от типа выполняемых задач. С увеличением объема вычислений должна расти и производительность компонентов, особенно процессора.

Основные преимущества блейд-серверов включают значительное снижение энергопотребления, повышение энергоэффективности и гибкость инфраструктуры благодаря модульной конструкции [2].

На энергопотребление сервера в первую очередь влияют его доступные ресурсы, такие как количество процессоров (и количество используемых ядер), их тактовая частота, объем оперативной памяти, производительность и емкость подсистемы хранения данных, а также производительность сетевых интерфейсов.

В зависимости от задачи цель подбора оборудования может заключаться как в увеличении доступных ресурсов, так и в их уменьшении. До определенного предела ресурсы наращиваются путем увеличения емкости и производительности памяти, а также числа процессоров. Однако дальнейшее наращивание таким способом становится неэффективным и экономически невыгодным. В таких случаях ресурсы увеличивают другими методами, например, распараллеливанием задач между несколькими серверами и оптимизацией приложения. Уменьшение ресурсов сервера обычно направлено на сокращение его размеров и потребляемой энергии [3].

#### ПРОЦЕССОР

Ключевые характеристики процессора [4] включают производительность, потребляемую мощность и энергетическую эффективность (среднее количество энергии, потребляемое на одну выполненную инструкцию).

Производительность процессора определяется как скорость выполнения инструкций программного

кода, т.е. количество инструкций, обработанных за единицу времени (instructions per second, IPS). Это можно выразить математически следующим образом:

Perfomance =

$$\frac{\text{Количество инструкций}}{\text{Время выполнения}} = \text{IPS.}$$

(1)

Вместо количества инструкций за единицу времени более удобно учитывать количество инструкций программного кода, выполняемых за один такт работы процессора (instructions per cycle, IPC).

$$\begin{aligned} \text{Perfomance} &= \frac{\text{Количество инструкций}}{\text{Количество тактов}} \times \\ &\times \frac{\text{Количество тактов}}{\text{Время выполнения}} = \text{IPC}. \end{aligned} \tag{2}$$

Производительность процессора напрямую зависит как от тактовой частоты F, так и от количества инструкций, выполняемых за один такт IPC.

Из этого следует, что существует два основных подхода к повышению производительности процессора [5]: первый – увеличение тактовой частоты, второй – увеличение числа инструкций, выполняемых за один такт. На практике обычно применяются оба подхода одновременно, т.к. параметры тактовой частоты и количество инструкций, выполняемых за такт, взаимосвязаны.

Зависимость потребляемой процессором мощности от его тактовой частоты выглядит следующим образом:

Power =

$$CU^2F$$

, (3)

где C — динамическая емкость процессора, U — напряжение питания процессора, F — рабочая частота процессора.

Иными словами, мощность, потребляемая процессором, пропорциональна тактовой частоте, квадрату напряжения питания процессора и его динамической емкости. Тактовая частота напрямую зависит от напряжения питания, поэтому потребляемая мощность изменяется с частотой процессора нелинейно. Следовательно, производительность и потребляемая мощность процессора также взаимосвязаны нелинейным образом.

Увеличение тактовой частоты дает лишь незначительный прирост производительности и при этом сопровождается значительно большим увеличением потребляемой мощности процессора [6].

В настоящее время акцент в повышении производительности процессоров сместился от увеличения тактовой частоты к достижению высокого уровня производительности при минимальном потреблении энергии. Ключевым показателем [7] в этом контексте является энергетическая эффективность процессора (energy per instruction, EPI), которая измеряется как среднее количество энергии, потребляемое на одну выполненную инструкцию:

$$EPI = \frac{Энергия (Дж)}{Количество инструкций}.$$

(4)

Производительность процессора в расчете на 1 ватт потребляемой мощности будет выглядеть так:

$$\frac{\frac{\text{Perfomance}}{\text{Power}} = \frac{\left(\frac{\text{Количество инструкций}}{\text{Время}}\right)}{\left(\frac{\text{Энергия}}{\text{Время}}\right)} = \frac{\left(\frac{\text{Количество инструкций}}{\text{Время}}\right)}{\frac{\text{Время}}{\text{Энергия}}} = \frac{1}{\text{EPI}}.$$

Соответственно:

$$EPI = \frac{Power}{Perfomance}.$$

(6)

Один из подходов к созданию энергоэффективного процессора заключается в использовании многоядерной архитектуры [8]. Это позволяет повысить производительность за счет увеличения числа инструкций, исполняемых за такт, без увеличения, а иногда и с уменьшением тактовой частоты. Теоретически, при увеличении числа ядер с 1 до 2 можно сохранить ту же производительность, снизив тактовую частоту каждого ядра в 2 раза.

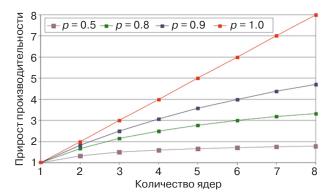

Прирост производительности в данном случае можно оценивать как сокращение времени выполнения программы при использовании многоядерного процессора tn по сравнению с временем ее выполнения на одноядерном процессоре t1. Таким образом, прирост производительности будет равен [9]:

$$\frac{t1}{tn} = 1 - p\left(1 - \frac{1}{n}\right),\tag{7}$$

где p — доля инструкций программного кода, способных выполняться параллельно; n — количество процессоров.

Графическая зависимость прироста производительности от числа ядер процессора показана на рис. 1.

**Рис. 1.** Зависимость прироста производительности от числа ядер процессора

Многоядерная архитектура значительно повышает производительность, особенно при одновременной работе нескольких приложений. В идеальных условиях каждое приложение может выполняться на отдельном ядре процессора.

#### Микропроцессоры IntelXeon

Микропроцессоры класса IntelXeon (Intel, США) [10] строятся на тех же микроархитектурах, что и процессоры (х86) для настольных систем, однако с добавлением специфических серверных черт.

Разработка процессоров для серверов отличается значительной сложностью по сравнению с настольными системами, поскольку серверные процессоры требуют внедрения множества специфических особенностей. Это делает процесс их разработки и внедрения более длительным и сложным. Несмотря на это, разница в техпроцессах между различными семействами процессоров, таких как Xeon, Opteron (AMD, США) и Baikal-T1 (Baikal Electronics, Россия), постепенно уменьшается. Это связано с увеличением сложности и времени разработки новых архитектур, использующих 10-нм технологический процесс.

Технология Crystalwell позволяет процессору преодолеть ограничения низкой пропускной способности системной памяти и продемонстрировать улучшенные результаты в обработке HD-видео и математических операциях. С использованием процессоров Broadwell возможно одновременное выполнение 4368 HD-видеопотоков, что на 40% больше по сравнению с 3120 потоками на процессорах Haswell.

Процессоры Intel Xeon E3 v6 представлены в 8 моделях, и ни одна из них не обладает пониженным энергопотреблением. В этой линейке также

отказались от использования eDRAM<sup>1</sup>. Процессоры с индексом 1xx5 v6, как и ранее, оснащены собственными графическими ядрами.

Основные изменения включают переход на архитектуру Kaby Lake при сохранении технологического процесса 14-нм. Кроме того, увеличена максимальная пропускная способность памяти до 37.5 ГБ/с, а также повышены частоты до DDR4-2400 и DDR3L-1866.

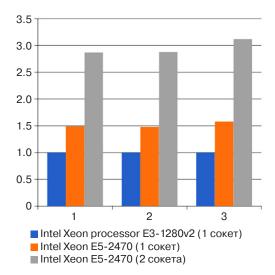

Прирост производительности при переходе от процессоров Е3 к Е5 и использовании двух процессоров Е5 отображен на рис. 2.

По тестам Intel наблюдается следующий результат: производительность увеличивается в 1.5 раза при переходе от процессоров ЕЗ к Е5 и еще в 2 раза при удвоении количества процессоров. Переход на 4-процессорную систему обеспечивает аналогичный линейный прирост производительности. Аналогично улучшается производительность и в новых поколениях процессоров, например, при переходе с ЕЗ v5 или v6 на Е5 v4.

**Рис. 2.** Изменение производительности при переходе от E3 к E5: 1 – SPECint\_ratebase 2006, 2 – SPECfp\*ratebase 2006, 3 –SPECjbb\*2005

В будущем процессоры Broadwell-EX будут заменены на Skylake Purley. Эти новые процессоры будут оснащены 6-канальными контроллерами оперативной памяти DDR4 (вместо 4-канальных у нынешнего поколения), набором инструкций AVX-512, шиной Omni-Path, поддержкой графики Cannonlake и встроенными FPGA<sup>2</sup>. Встроенные FPGA позволяют оптимизировать конфигурацию процессора под конкретные задачи, что не предусмотрено в архитектуре Skylake.

#### Процессоры Intel Xeon D

Процессоры Intel Xeon D [11] являются преемниками линейки Atom, но предназначены для легких серверных решений. Эти процессоры представляют собой системы на кристалле (SoC³) и включают вычислительные ядра х86, сетевую карту 10G, порты ввода-вывода (включая PCIe⁴), контроллер DDR4 и интерфейсы SATA. Они изготавливаются с использованием 14-нм технологического процесса.

Intel Xeon D-15xx предлагают новые возможности оптимизации разнообразных рабочих нагрузок и инфраструктур.

Сейчас их основная область применения — это сетевые системы, облачные хранилища и корпоративные системы хранения данных.

#### Серверные процессоры AMD Opteron

Серверные процессоры от AMD представлены пятью сериями: Opteron 3000, 4000 и 6000, А-серией на основе ARM-архитектуры, а также гибридными процессорами X-серии [12]. Эти процессоры предназначены для веб-хостинга и характеризуются доступной ценой. Они поддерживают память DDR3-1866 МГц.

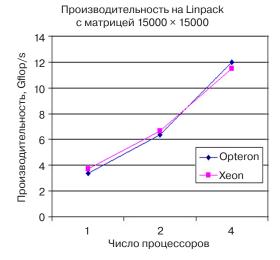

В целом, линейка процессоров Opteron обеспечивает хорошую производительность, большое количество ядер и конкурентоспособную цену. Процессоры Opteron не используют аналоги технологии Hyperthreading; их производительность увеличивается за счет добавления большего числа физических ядер.

**Puc. 3.** Сравнение производительности процессоров Intel Xeon и AMD Opteron

<sup>&</sup>lt;sup>1</sup> Embedded dynamic random access memory – встраиваемая динамическая память с произвольным доступом.

<sup>&</sup>lt;sup>2</sup> Field-programmable gate array – программируемые пользователем вентильные матрицы.

<sup>&</sup>lt;sup>3</sup> System-on-a-chip.

<sup>&</sup>lt;sup>4</sup> Peripheral component interconnect express – компьютерная шина, обеспечивающая соединение «точка-точка» при помощи высокопроизводительного протокола последовательной передачи данных. [Peripheral component interconnect express is a computer bus that provides point-to-point connectivity using a high-performance serial communications protocol.]

Созданный на основе процессора X2150 гибридный процессор X2170 представляет собой полностью интегрированный блок с архитектурой х86, который включает центральный процессор, графический процессор и контроллер ввода/вывода. Он отличается низким энергопотреблением, что позволяет снизить общую стоимость владения центрами обработки данных и адаптироваться к требованиям высокопроизводительных серверных платформ.

Основные задачи, для которых предназначены эти серверные процессоры, включают организацию сетей доставки и дистрибуции, предварительную обработку видео, консольные десктоп-клиенты, рендеринг, перекодировку и потоковую передачу видео.

Объединение технологий центрального и графического процессоров в сверхплотном форм-факторе может привести к большому выигрышу в расчете производительности на 1 ватт по сравнению с традиционными решениями.

#### Процессор Baikal-T1

Процессор Baikal-T1 [13] основан на 2 вычислительных ядрах с тактовой частотой 1.2 ГГц, выполненных по 28-нм технологическому процессу и относящихся к семейству MIPS Warrior P5600 г5 компании Imagination Technologies (Великобритания). Он использует архитектуру MIPS32 с поддержкой парадигмы внеочередного исполнения команд и возможностью объединения до 6 ядер в единый кластер. Ядра P5600 г5 поддерживают технологию аппаратной зональной защиты данных OmniShield и 128-разрядные SIMD-команды<sup>5</sup> для высокоскоростной обработки параллельных вычислений, особенно в мультимедийных приложениях.

Процессор оснащен 1 Мб высокопроизводительной когерентной кэш-памяти и встроенным контроллером оперативной памяти с поддержкой DDR3-1600. Он включает в себя интегрированные интерфейсы:  $1 \times 10$  Гбит Ethernet,  $2 \times 1$  Гбит Ethernet, PCIe Gen.3 x4, SATA 3.0 и USB 2.0. Энергопотребление процессора не превышает 5 Вт, что позволяет создавать бесшумные системы, не требующие активного охлаждения.

Основные ожидаемые области применения данного процессора – промышленная автоматика, встроенные системы, коммуникации.

#### ОПЕРАТИВНАЯ ПАМЯТЬ

Серверная память отличается от настольной тем, что она обычно включает модули с контролем

четности и коррекцией ошибок (error correction code, ECC). Такая память часто обладает дополнительной функциональностью, направленной на обеспечение большей стабильности, например, использование регистровой буферизированной памяти. Серверная память создается по стандартам, отличным от тех, что применяются в настольных системах.

Ключевой характеристикой серверной оперативной памяти является отказоустойчивость. Многие серверы предназначены для работы критически важных приложений, которые предъявляют повышенные требования к памяти. Уровень отказоустойчивости обеспечивается как за счет усовершенствования процесса производства микросхем, так и за счет использования технологий защиты памяти от ошибок, таких как ECC [14].

Существует два основных способа защиты от ошибок памяти:

- 1. Тестирование модулей регулярная проверка состояния памяти для выявления и устранения проблем.

- 2. Использование технологий обнаружения и исправления ошибок внедрение технологий, которые автоматически обнаруживают и исправляют ошибки памяти.

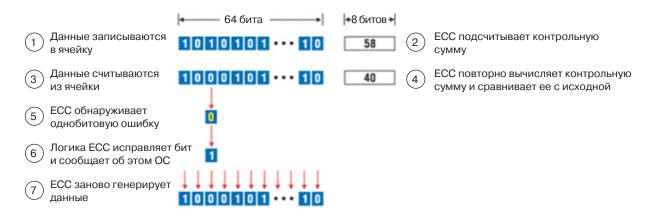

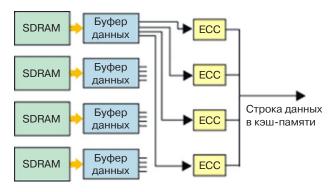

Технология ЕСС значительно снижает вероятность ошибок памяти. Она обеспечивает обнаружение и исправление однобитовых ошибок и обнаружение многобитовых ошибок. Это важная функция для серверной оперативной памяти, где надежность и устойчивость к ошибкам критически важны. Механизм работы продемонстрирован на рис. 4.

Ошибки памяти могут также приводить к значительным простоям в приложениях серверов баз данных. В случае возникновения ошибки восстановление базы данных может занять несколько часов, т.к. серверу потребуется восстановить данные на основании записей журнала транзакций, которые еще не были занесены в базу данных.

Технология Advanced ECC предназначена для исправления многобитовых ошибок в одной микросхеме DRAM. Она обеспечивает возможность восстановления данных даже в случае отказа всей микросхемы, что значительно повышает надежность системы.

Четыре разряда от каждой микросхемы распределяются по четырем устройствам ЕСС (по одному разряду для каждого устройства ЕСС), поэтому при ошибке в одной микросхеме возможно исправление до четырех однобитовых ошибок (рис. 5).

Для борьбы с многоразрядными ошибками на отдельных микросхемах, включая сбой всех разрядов данных, используется механизм Chipkill. Этот механизм обеспечивает более высокую защиту

<sup>&</sup>lt;sup>5</sup> Single instruction, multiple data – принцип компьютерных вычислений, позволяющий обеспечить параллелизм на уровне данных. [Single instruction, multiple data – a principle of computer computing that enables parallelism at the data level.]

Рис. 4. Схема обнаружения и исправления однобитовой ошибки. ОС – операционная система

Рис. 5. Схема работа AdvancedECC

и надежность по сравнению с традиционными методами.

На данный момент DDR4 DRAM является наиболее передовой и широко используемой технологией оперативной памяти. Однако DDR5 DRAM уже находится в стадии разработки. Ожидается, что DDR5 обеспечит вдвое большую емкость модулей по сравнению с DDR4, а также увеличит пропускную способность. Память DDR5 будет производиться по 10-нм технологическому процессу и первоначально будет иметь объем от 1 до 4 ГБ.

#### ПОДСИСТЕМА ХРАНЕНИЯ

Важным аспектом является доступность накопителей: серверные накопители должны оставаться функциональными и активными в любое время, тогда как накопители настольных персональных компьютеров могут быть переведены в режим «ожидания», если доступ к ним не требуется [15].

Для обеспечения надежности и производительности часто применяются RAID-массивы<sup>6</sup>, которые объединяют несколько дисковых накопителей для повышения отказоустойчивости и производительности. Важными факторами, влияющими на выбор накопителей, являются интерфейс подключения, ем-

кость и структура накопителя. Также значительную роль играют предполагаемые данные, которые будут храниться, их важность и требования установленных приложений.

Жесткие диски (hard disk drive, HDD) являются классическим решением для хранения данных. Они предоставляют приемлемый уровень надежности, а их производительность зависит от таких факторов, как скорость вращения, интерфейс и размер кэша. Скорость вращения жестких дисков варьируется от 7200 до 15000 оборотов в минуту в зависимости от требований к производительности. Однако увеличение скорости вращения приводит к большему энергопотреблению и более высоким требованиям к системе охлаждения. Дополнительной проблемой могут стать вибрации, возникающие из-за вращения дисков с различной скоростью, что может нарушить их работу, если диски находятся в разных циклах записи. Для предотвращения подобных проблем рекомендуется использовать диски с одинаковой скоростью вращения в рамках одного сервера. Также стоит отметить, что срок службы жестких дисков ограничен их механическим износом.

Твердотельные накопители (solid state drive, SSD) не имеют подвижных частей, что исключает механический износ и вибрации. Они используют флеш-память для хранения данных, что позволяет им достигать производительности ввода/вывода, которая может в сотни раз превосходить производительность жестких дисков. Кроме того, SSD потребляют примерно пятую часть энергии по сравнению с HDD, т.к. им не требуется питание для электродвигателя.

При выборе накопителей важно учитывать, что твердотельные накопители имеют ограниченный срок хранения данных в выключенном состоянии. В случае использования таких накопителей для резервного хранения данных информация будет доступна не более 10 лет. Этот срок может быть сокращен из-за интенсивного использования накопителя и воздействия окружающей температуры.

<sup>&</sup>lt;sup>6</sup> Redundant array of independent disks.

Перспективным направлением в развитии систем хранения данных является переход на энергонезависимую память типа NAND<sup>7</sup>. Такая память устраняет основные причины задержек в канале обмена данными между системой и полупроводниковым накопителем. Использование шины PCIе непосредственно, без дополнительных адаптеров (SATA, SAS и др.), позволяет уменьшить латентность на уровне контроллера. Выбор NVMe<sup>8</sup> помогает устранить задержки на уровне программного обеспечения (как в микропрограмме контроллера, так и в системных драйверах) и значительно увеличивает уровень параллелизма при обмене потоками данных по шине.

Интерфейс NVMe является ключевым преимуществом для серверных приложений, особенно при обработке большого количества запросов одновременно. Переход к NVMe позволяет значительно повысить эффективность работы с дисковыми массивами за счет масштабирования числа очередей и команд.

Разработка новых технологий хранения данных, таких как PCM<sup>9</sup> и другие перспективные решения, обещает продолжить эволюцию систем хранения и может в будущем привести к значительным улучшениям в скорости доступа и общей производительности.

По оценкам компании Crossbar, модули RRAM<sup>10</sup> обеспечат скорость записи, в 20 раз превосходящую скорость флеш-памяти NAND, достигая 140 Мб/с по сравнению с 7 Мб/с у NAND. Скорость чтения для RRAM составит около 17 Мб/с. Дополнительным преимуществом RRAM является долговечность хранения данных, которая может составлять до 20 лет,

в то время как у NAND этот срок составляет всего 1–3 года.

В качестве альтернативы флеш-памяти NAND также рассматривается магниторезистивная память (magnetoresistive random-access memory, MRAM). Она выделяется высокой скоростью доступа к данным и надежностью при неблагоприятных внешних условиях. Магниторезистивная память способна функционировать при очень высоких температурах, что делает ее особенно подходящей для использования в экстремальных условиях, таких как военные и космические приложения.

#### выводы

Проведенный обзор вариантов организации серверов и их основных составляющих позволяет сделать вывод о достаточно высокой надежности их функционирования. Однако от серверов, объединенных в ВС класса WSC (warehouse scale computer), как от системы, требуется нечто большее, а именно, непрерывность функционирования в режиме 24/7 в течение длительного времени. Это, в свою очередь, требует разработки методик оценки надежности таких высоконадежных систем, включающих резервные элементы, по отношению к отказам аппаратуры и программного обеспечения, а также методик прогнозирования отказов и мер борьбы с их последствиями.

#### Вклад авторов

Все авторы в равной степени внесли свой вклад в исследовательскую работу.

#### **Authors' contribution**

All authors equally contributed to the research work.

#### СПИСОК ЛИТЕРАТУРЫ

- 1. Хенесси Д.Л., Паттерсон Д.А. *Компьютерная архитектура. Количественный подход.* 5-е изд. М.: Техносфера; 2016. 936 с.

- 2. Сугак Е.В. Прикладная теория надежности. Практикум. М.: Лань; 2023. 312 с. ISBN 978-5-507-47014-3

- 3. Тенгайкин Е.И. Организация сетевого администрирования. Сетевые операционные системы, серверы, службы и протоколы. Практические работы. СПб.: Лань; 2022. 100 с. ISBN 978-5-8114-9783-6

- 4. Коваленко С.М., Платонова О.В. Анализ задачи эффективной эксплуатации комплексов систем автоматизации и расчеты надежности на основе непрерывных моделей. *Известия вузов. Машиностроение*. 2014;8(653):75–89. http://doi.org/10.18698/0536-1044-2014-8-75-79

- 5. Воеводин В.В., Воеводин Вл.В. Параллельные вычисления. СПб.: БХВ-Петербург; 2002. 608 с.

- 6. Орлов С.А., Цилькер Б.Я. Организация ЭВМ и систем. СПб.: Питер; 2016. 688 с.

<sup>&</sup>lt;sup>7</sup> Not AND – универсальный двухвходовый логический элемент, штрих Шеффера. [Not AND is a universal two-input logic element, Schaeffer stroke.]

<sup>&</sup>lt;sup>8</sup> NVM Express – от англ. non-volatile memory host controller interface specification – интерфейс доступа к твердотельным накопителям, подключенным по шине PCI Express. [ NVM Express is non-volatile memory host controller interface specification—access interface to solid state drives connected via PCI Express bus.]

<sup>&</sup>lt;sup>9</sup> Pulse code modulation – импульсно-кодовая модуляция.

$<sup>^{10}</sup>$  Resistive random-access memory – резистивная память с произвольным доступом.

- 7. Половко А.М., Гуров С.В. Основы теории надежности. СПб.: БХВ-Петербург; 2006. 702 с. ISBN 5-94157-541-6

- 8. Черкесов Г.Н. Надежность аппаратно-программных комплексов. СПб.: Питер; 2005. 479 с. ISBN 5-469-00102-4

- 9. Сапожников В.В., Сапожников В.В., Ефанов Д.В. *Основы теории надежности и технической диагностики*. СПб.: Лань; 2019. 588 с. ISBN 978-5-8114-3453-4

- 10. Podgorny Y.V., Antonovich A.N., Petrushin A.A., Sigov A.S., Vorotilov K.A. Effect of metal electrodes on the steady-state leakage current in PZT thin film capacitors. *J. Electroceram*. 2022;49:15–21. https://doi.org/10.1007/s10832-022-00288-5

- 11. Абдуллаев Д.А., Милованов Р.А., Волков Р.Л., Боргардт Н.И., Ланцев А.Н., Воротилов К.А., Сигов А.С. Сегнетоэлектрическая память: современное производство и исследования. *Российский технологический журнал*. 2020;8(5):44–67. https://doi.org/10.32362/2500-316X-2020-8-5-44-67

- 12. Конюхова О.В., Кравцова Э.А., Лукьянов П.В. *Техническое и программное обеспечение вычислительных машин и систем*. М., Вологда: Инфра-Инженерия; 2023. 200 с. ISBN 978-5-9729-1186-8

- 13. Журавлев А.А. *Организация и архитектура ЭВМ. Вычислительные системы*. СПб.: Лань; 2022. 144 с. ISBN 978-5-507-48089-0

- 14. Гельбух С.А. Сети ЭВМ и телекоммуникации. Архитектура и организация. СПб.: Лань; 2019. 208 с. ISBN 978-5-8114-3474-9

- 15. Андреев А.М., Можаров Г.П., Сюзев В.В. *Многопроцессорные вычислительные системы. Теоретический анализ, математические модели и применение*. М.: Издательство МГТУ им. Н.Э. Баумана; 2011. 336 с. ISBN 978-5-7038-3439-6

#### **REFERENCES**

- 1. Henessey J.L., Patterson D.A. *Komp'yuternaya arkhitektura. Kolichestvennyi podkhod (Computer Architecture. A Quantitative Approach*): transl. from Engl. 5th ed. Moscow: Tekhnosfera; 2016. 936 p. (in Russ.). [Henessey J.L., Patterson D.A. *Computer Architecture. A Quantitative Approach.* 5th ed. Morgan Kaufmann; 2011. 856 p.]

- 2. Sugak E.V. *Prikladnaya teoriya nadezhnosti. Praktikum (Applied Reliability Theory. The Workshop. Textbook).* Moscow: Lan; 2023. 312 p. (in Russ.). ISBN 978-5-507-47014-3

- 3. Tengaikin E.I. Organizatsiya setevogo administrirovaniya. Setevye operatsionnye sistemy, servery, sluzhby i protokoly. Prakticheskie raboty (Organization of Network Administration. Network Operating Systems, Servers, Services and Protocols. Practical Work). St. Petersburg: Lan; 2022. 100 p. (in Russ.). ISBN 978-5-8114-9783-6

- 4. Kovalenko S.M., Platonova O.V. Analysis of the operational efficiency of complex automation systems and the calculation of their reliability on the basis of continuous models. *Izvestiya vysshikh uchebnykh zavedenii*. *Mashinostroenie* = *BMSTU J*. *Mechanical Engineering*. 2014;8(653):75–89 (in Russ.). http://doi.org/10.18698/0536-1044-2014-8-75-79

- 5. Voevodin V.V., Voevodin VI.V. *Parallel'nye vychisleniya (Parallel Computing)*. St. Petersburg: BHV-Petersburg; 2002. 608 p. (in Russ.).

- 6. Orlov S.A., Tsil'ker B.Ya. *Organizatsiya EVM i system (Organization of Computers and Systems)*. St. Petersburg: Piter; 2016. 688 p. (in Russ.).

- 7. Polovko A.M., Gurov S.V. *Osnovy teorii nadezhnosti (Fundamentals of Reliability Theory*). St. Petersburg: BHV-Petersburg; 2006. 702 p. (in Russ.). ISBN 5-94157-541-6

- 8. Cherkesov G.N. *Nadezhnost' apparatno-programmnykh kompleksov (Reliability of Hardware and Software Complexes)*. St. Petersburg: Piter; 2005. 479 p. (in Russ.). ISBN 5-469-00102-4

- 9. Sapozhnikov V.V., Sapozhnikov V.V., Efanov D.V. Osnovy teorii nadezhnosti i tekhnicheskoi diagnostiki (Fundamentals of Reliability Theory and Technical Diagnostics). St. Petersburg: Lan; 2019. 588 p. (in Russ.). ISBN 978-5-8114-3453-4

- 10. Podgorny Y.V., Antonovich A.N., Petrushin A.A., Sigov A.S., Vorotilov K.A. Effect of metal electrodes on the steady-state leakage current in PZT thin film capacitors. *J. Electroceram.* 2022;49:15–21. https://doi.org/10.1007/s10832-022-00288-5

- 11. Abdullaev D.A., Milovanov R.A., Volkov R.L., Borgardt N.I., Lantsev A.N., Vorotilov K.A., Sigov A.S. Ferroelectric memory: state-of-the-art manufacturing and research. *Rossiiskii tekhnologicheskii zhurnal*. 2020;8(5):44–67 (in Russ.). https://doi.org/10.32362/2500-316X-2020-8-5-44-67

- 12. Konyukhova O.V., Kravtsova E.A., Lukyanov P.V. *Tekhnicheskoe i programmnoe obespechenie vychislitel'nykh mashin i system (Technical and Software Support of Computers and Systems)*. Moscow, Vologda: Infra-Inzheneriya; 2023. 200 p. (in Russ.). ISBN 978-5-9729-1186-8

- 13. Zhuravlev A.A. Organizatsiya i arkhitektura EVM. Vychislitel'nye sistemy (Organization and Architecture of Computers. Computer Systems). St. Petersburg: Lan; 2022. 144 p. (in Russ.). ISBN 978-5-507-48089-0

- 14. Gelbukh C.A. Seti EVM i telekommunikatsii. Arkhitektura i organizatsiya (Computer Networks and Telecommunications. Architecture and Organization). St. Petersburg: Lan; 2019. 208 p. (in Russ.). ISBN 978-5-8114-3474-9

- 15. Andreev A.M., Mozharov G.P., Syuzev V.V. *Mnogoprotsessornye vychislitel'nye sistemy. Teoreticheskii analiz, matematicheskie modeli i primenenie (Multiprocessor Computing Systems. Theoretical Analysis, Mathematical Models and Applications)*. Moscow: Bauman Press; 2011. 336 p. (in Russ.). ISBN 978-5-7038-3439-6

#### Об авторах

**Петушков Григорий Валерьевич,** проректор, ФГБОУ ВО «МИРЭА – Российский технологический университет» (119454, Россия, Москва, пр-т Вернадского, д. 78). E-mail: petushkov@mirea.ru. https://orcid.org/0009-0006-0801-429X

**Сигов Александр Сергеевич,** академик Российской академии наук, д.ф.-м.н., профессор, президент ФГБОУ ВО «МИРЭА – Российский технологический университет» (119454, Россия, Москва, пр-т Вернадского, д. 78). E-mail: sigov@mirea.ru. Scopus Author ID 35557510600, ResearcherID L-4103-2017, SPIN-код РИНЦ 2869-5663, www.researchgate.net/profile/A\_Sigov

#### **About the authors**

**Grigory V. Petushkov,** Vice-Rector, MIREA – Russian Technological University (78, Vernadskogo pr., Moscow, 119454 Russia). E-mail: petushkov@mirea.ru. https://orcid.org/0009-0006-0801-429X

**Alexander S. Sigov,** Academician at the Russian Academy of Sciences, Dr. Sci. (Phys.-Math.), Professor, President, MIREA – Russian Technological University (78, Vernadskogo pr., Moscow, 119454 Russia). E-mail: sigov@mirea.ru. Scopus Author ID 35557510600, ResearcherID L-4103-2017, RSCI SPIN-code 2869-5663, https://www.researchgate.net/profile/A\_Sigov